頂部散熱封裝QDPAK簡介

QDPAK頂部散熱器是一種表貼裝置產品。相對於傳統表貼產品只能從底部進行散熱的方式,頂部散熱器分離了電氣路徑和熱流路徑,特別適合在高功率密度的應用,如車載充電器和AI伺服器電源等應用。而英飛凌不久前推出的QDPAK封裝也是目前英飛凌量產的封裝中最大尺寸的頂部散熱產品。

QDPAK頂部散熱器是一種表貼裝置產品。相對於傳統表貼產品只能從底部進行散熱的方式,頂部散熱器分離了電氣路徑和熱流路徑,特別適合在高功率密度的應用,如車載充電器和AI伺服器電源等應用。而英飛凌不久前推出的QDPAK封裝也是目前英飛凌量產的封裝中最大尺寸的頂部散熱產品。

QDPAK封裝目前包含600V,650V,750V,1200V電壓等級的SiC MOSFET產品和部分電壓的IGBT產品。

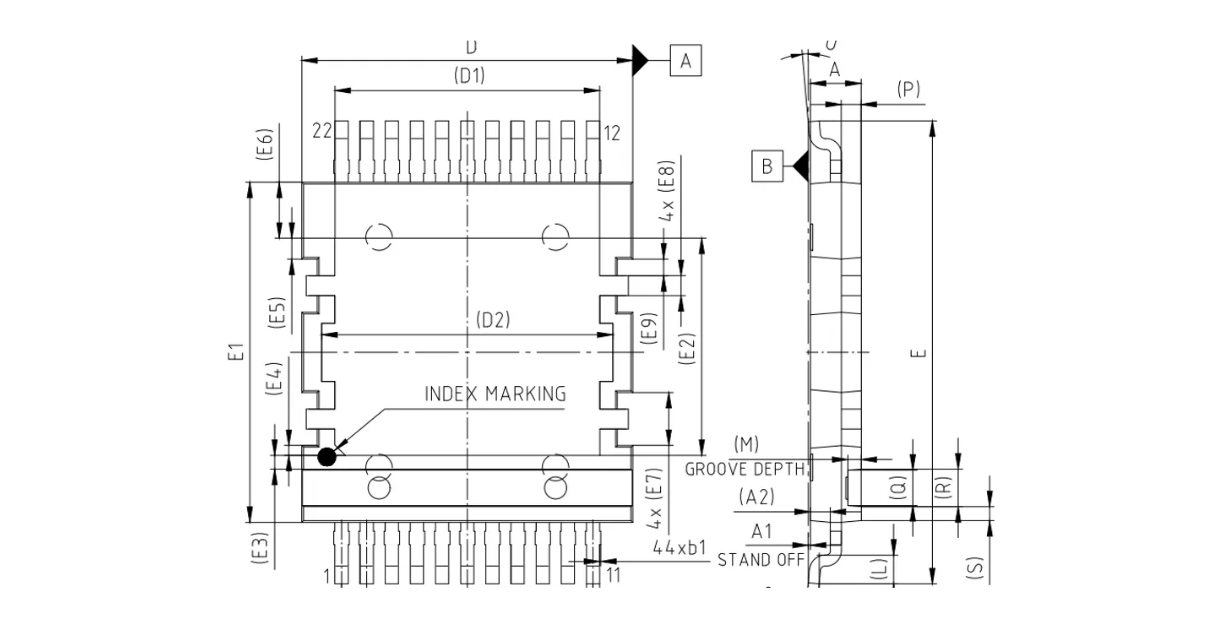

QDPAK目前已成功註冊為JEDEC標準,封裝尺寸為15mm*21mm,高度2.3mm,如下圖:

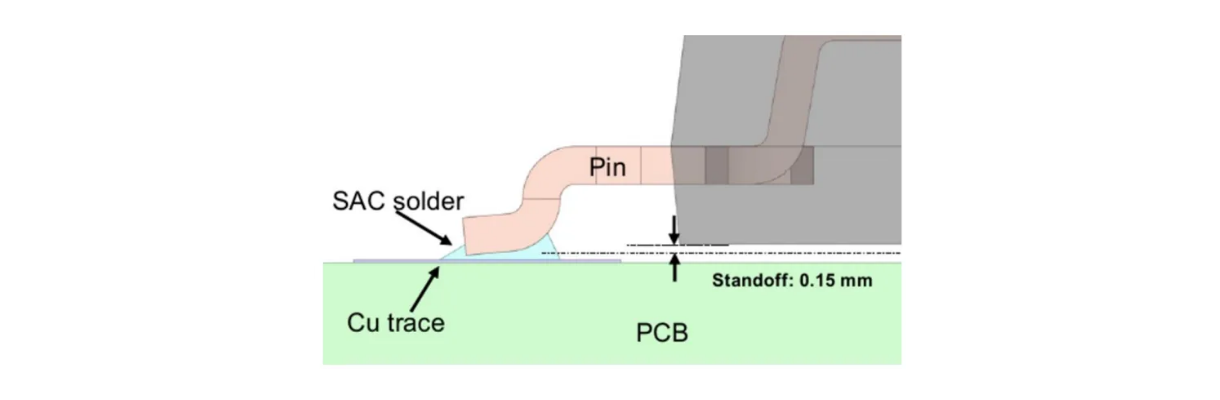

如⬆️圖:塑封本體與封裝接腳邊緣之間存在最大0.15mm間隔,這樣帶來的好處是:

▪︎ 首先,鋼網印製錫膏後,接腳會先接觸錫膏,確保焊接的可靠性,使用者只需要把裝置放置於PCB上即可進行回流焊接。

▪︎ 其次,這個間隔可以允許少量異物存在本體下方而不需要對PCB做特別的清潔。

▪︎ 最後,由於接腳先接觸PCB,接腳可以作為彈簧的特性,能緩解一部分塑封本體受力引起的形變。

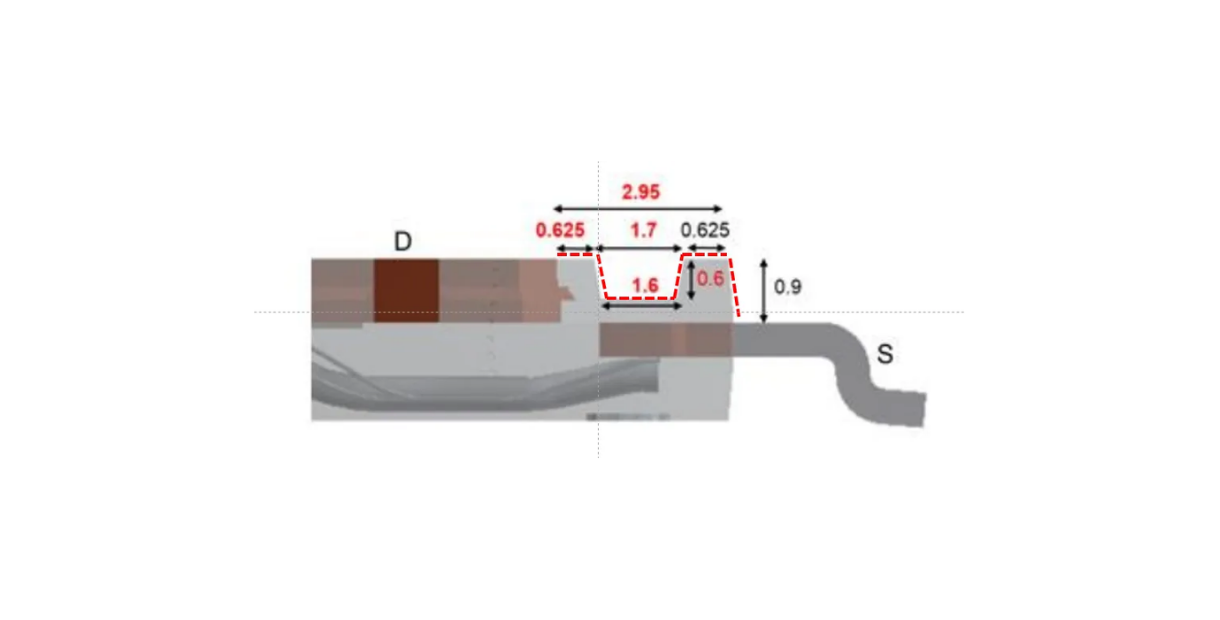

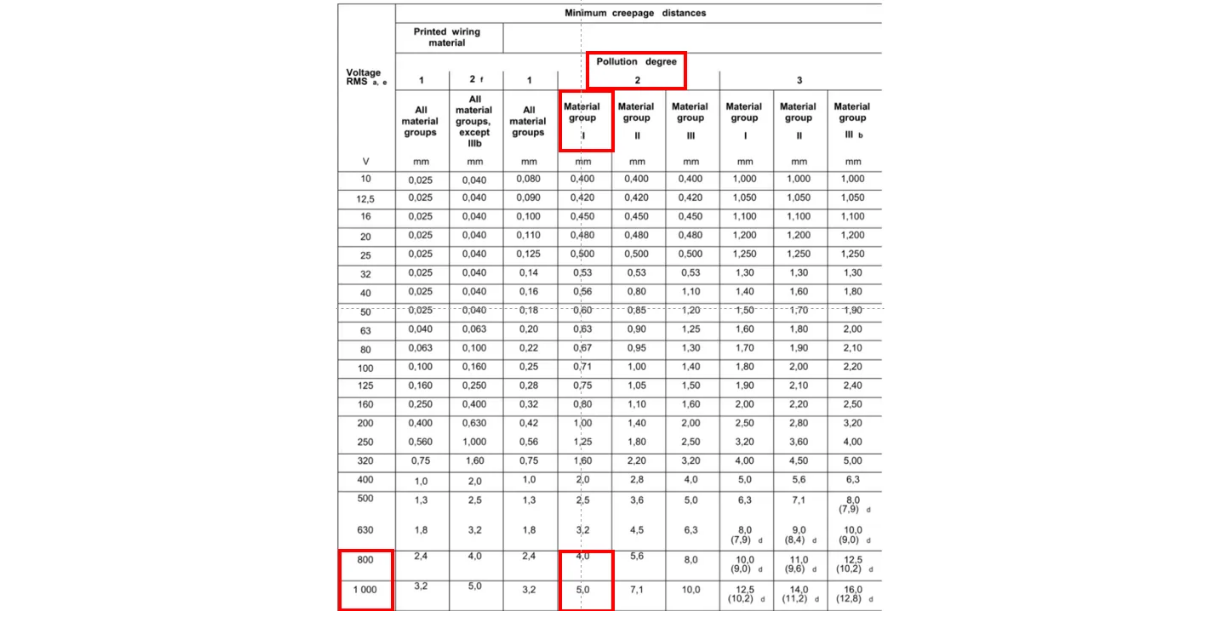

如下圖,裝置本體D極到S極的爬電距離大於4.8mm,如下圖虛線部分。另外,元件本體使用塑封材料屬於Ⅰ類材料組,CTI≥600,根據IEC60664標準,如下表,污染等級為2的類別下,800-1000Vrms工作電壓對應最小爬電距離為4-5mm,考慮一定裕量和包裹爬電尺寸的誤差,本絕緣可滿足在950VVrmrm voltage定義請參考IEC相關標準)。

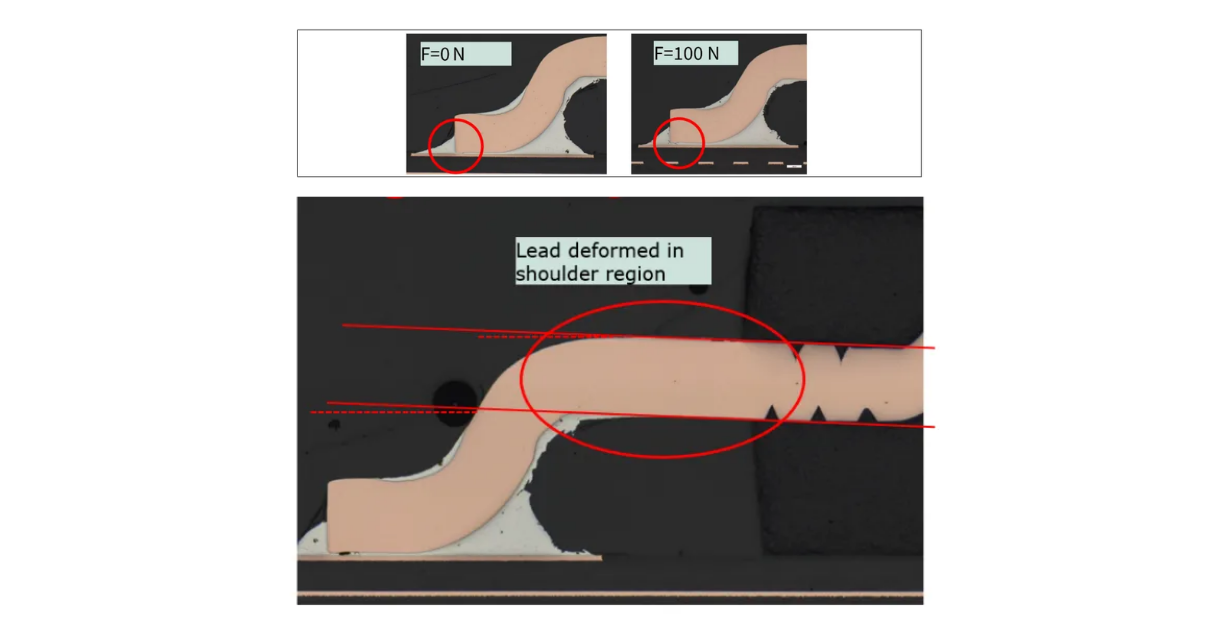

為了驗證封裝的可靠性,英飛凌同時進行了兩項不同的研究實驗。第一組測試板在標準FR4電路板上焊接裝置;第二組測試板在標準FR4電路板上焊接裝置後,也另外對每個裝置頂部垂直施加100N的壓力。隨後對兩組樣本進行板載溫度循環(TCoB)測試,以探討外部作用力對封裝結構TCoB魯棒性的影響。

如下圖一,展示了兩組樣本的焊點狀態。可以清楚觀察到:額外施加的作用力並未改變焊點連接狀態,應力未被直接傳導。封裝接腳發揮彈簧效應吸收了作用力,其形變主要發生在封裝肩部區域,如下圖二。後續裝置檢測表明,在經歷溫度循環後,受外力作用的第二組樣品的焊點比無外力作用的第一組的焊點承受更大應力。但兩組樣本在2000次以上TCoB循環中均未出現失效,證明無論裝置有無承受外力,都具有極高的可靠性和機械穩定性,這種卓越的TCoB可靠性可歸因於封裝的彈簧特性。

綜上所述,英飛凌QDPAK封裝透過頂部散熱的高可靠性,正成為電動車和高功率密度電源系統的理想選擇。其優勢已在CoolSiC™系列中驗證,未來隨著JEDEC標準的普及,將進一步推動高效、緊湊的電源系統發展。

由於QDPAK封裝是英飛凌新一代高功率產品的表貼頂部散熱產品,其安裝方式有所不同,所以針對其安裝方式做一些詳細的介紹。

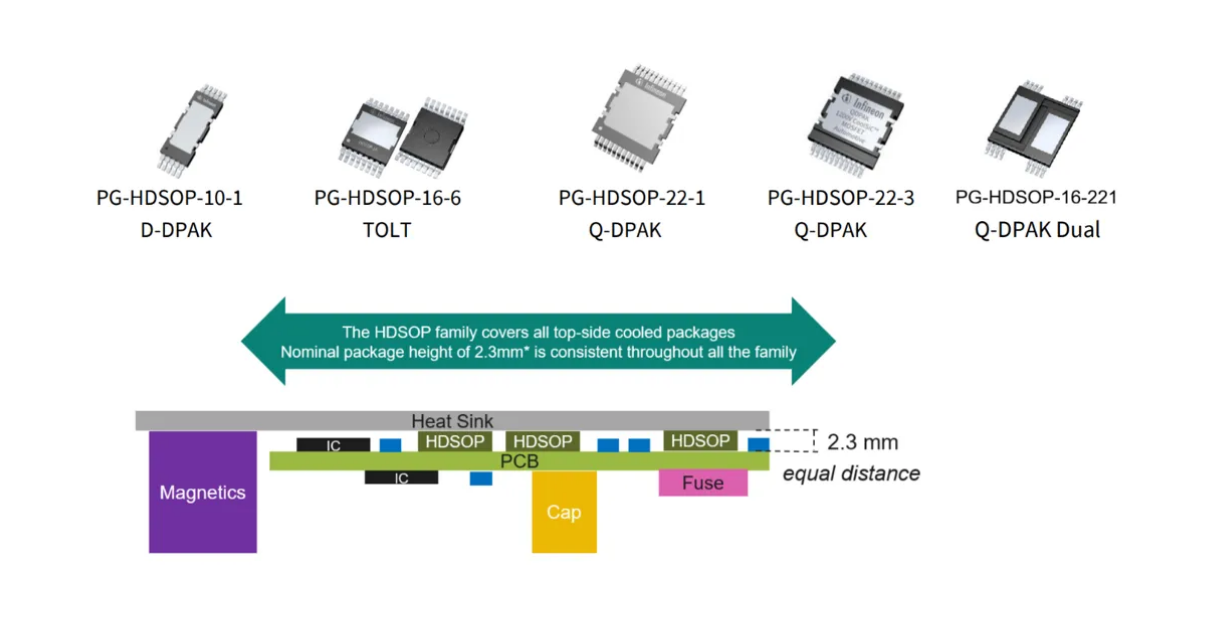

如下圖,英飛凌針對600V以上高壓元件推出了HDSOP封裝系列(D-DPAK, TOLT, 及QDPAK) 。如下圖列出了該系列已發布的封裝型號及其關鍵參數資訊。所有封裝均具有統一的2.3mm標準本體厚度,此特性使得不同分立元件(如650V碳化矽二極體、高壓/低壓MOSFET等)可混合安裝在同一散熱板上。

設計優化了組裝流程:所有功率元件在PCB上的安裝位置到散熱板頂面的距離保持一致,既簡化了組裝工序,又無需對散熱板進行特殊結構處理。

*QDPAK封裝中22-3在22-1塑封本體上增加了一個凹槽,加大了D與S的爬電距離。

將表貼頂部散熱封裝元件單獨安裝到散熱器上相對容易,由於機械公差無需特別考慮,因此,本文檔不涉及單裝置獨立散熱器的安裝說明。在實際應用過種中,QDPAK可以支援更高的功率輸出,因為通常會有多個QDPAK或頂部散熱器件安裝在同一個散熱器上。為優化散熱性能,建議盡可能減少PCB翹曲。可透過以下方式實現:

➊ 控制PCB尺寸-尺寸越大,翹曲越明顯。或使用硬度更高或更厚的PCB減少板子本身形變。

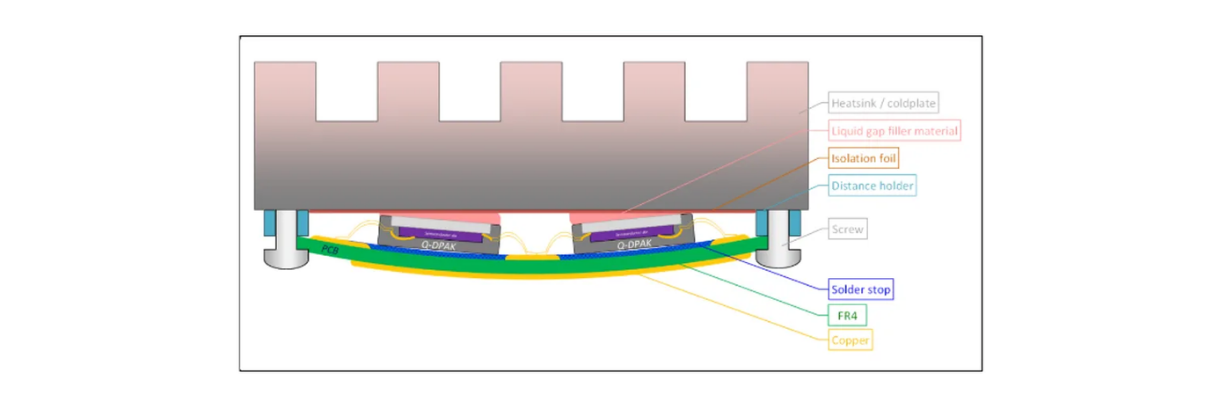

➋ 增加分佈式機械接觸點,透過多點支撐有效降低PCB形變,如下圖箭頭所示,除了散熱器四個角落有螺絲加以固定之外。每個QPDAK封裝兩側都有兩個螺絲加以固定,以減少PCB的形變。

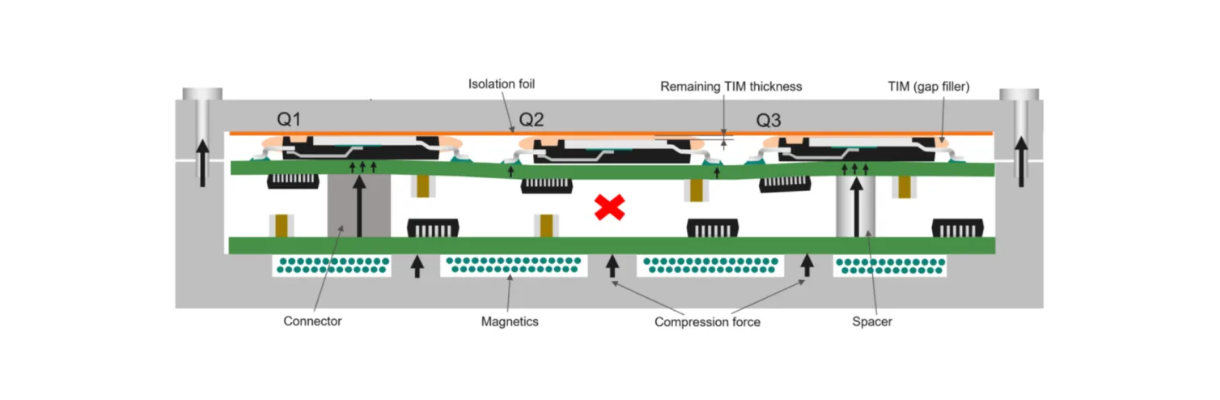

如下圖,展示了透過螺絲簡化PCB與散熱器組裝的範例。在兩個QDPAK封裝之間缺少螺絲的位置,可能出現PCB翹曲,這將導致界面導熱材料殘留厚度過大,進而增大熱接觸熱阻,導致結溫偏高。

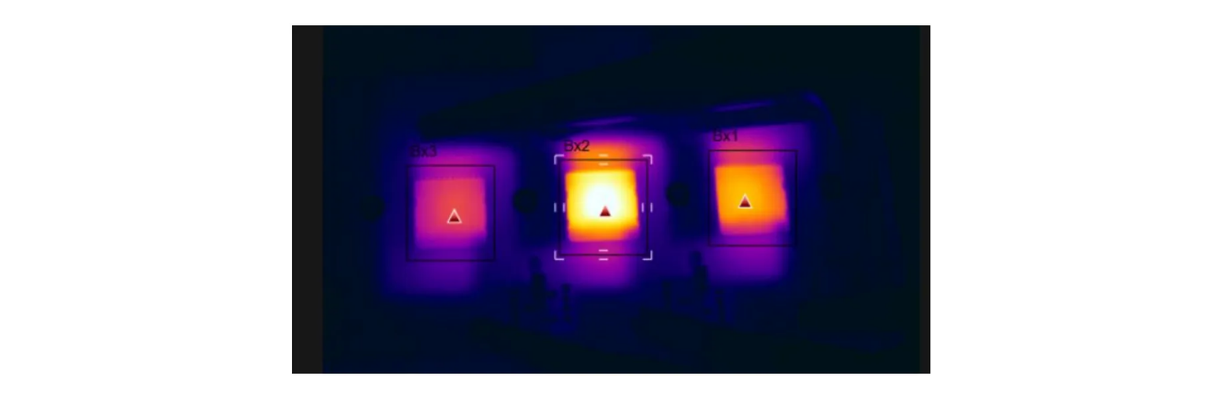

下圖是實際溫升測試,由於裝置之間沒有使用螺絲固定,在形變最大的中間位置,QDPAK元件的溫度最高。

然而,若透過增加過多螺絲及對應PCB鑽孔來解決此問題,又會在功率佈線最關鍵區域造成導電面積損失。

所以,第三種方式是採用剛性基材或加裝金屬承載結構在PCB下方進行機械加強措施。如下圖:

透過PCB背面的支撐柱和連接器對功率PCB施加壓力。此設計確保了外殼上下部分具有足夠的剛度,在向封裝施加足夠壓力的同時最小化外殼變形。理想情況下,每個封裝都應單獨施加壓力。否則,缺少支撐柱的裝置(下圖Q2所示)會導致界面導熱材料殘留厚度增大,進而使熱阻升高。

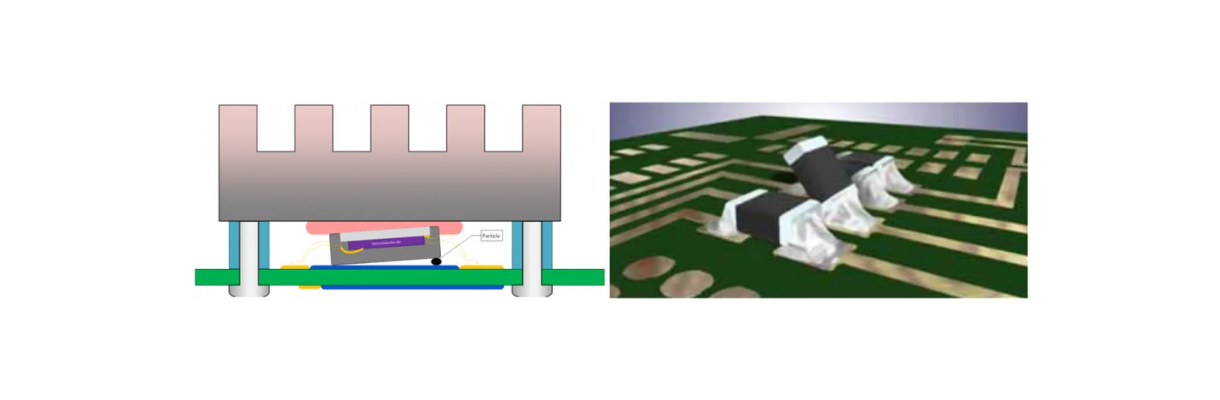

而對於裝置層面,表貼產品在組裝過程中,清潔電路板可有效防止功率元件底部異物顆粒所造成的意外傾斜(如下左圖)。由於Q-DPAK的接腳與本體底面的正公差設計,即使不對電路板做特別清潔,也會大幅減少這種情況的發生機率。另外,回流焊接製程可能引發的SMD元件傾斜效應(如"立碑"現象,如下右圖)也應予以避免。

綜上所述,針對QDPAK封裝,為最大限度的發揮其頂部散熱性能,在保證合理的壓力情況下,PCB和器件層面都要盡可能保持平整,減小因為器件傾斜或者PCB的翹曲引起的界面導熱材厚度偏大而造成的器件溫度偏高的情況。

如您有興趣得產品想要了解,請填寫以下表單,我們誠摯的歡迎您的訊息

STEP

STEP

Total 0

聯繫電話

姓名、 稱謂、 公司名稱、 聯繫電話、 E - Mail 、 主旨、 驗證碼 欄位格式輸入錯誤

姓名

稱謂

公司名稱

聯繫電話

主旨

其他問題